# XD6121/XD6122 XD6123/XD6124 Series

ETR02040-007a

Voltage Detector with Watchdog Function and ON/OFF Control

AEC-Q100 Grade3

### **■**GENERAL DESCRIPTION

The XD6121/XD6122/XD6123/XD6124 series is a group of high-precision, low current consumption voltage detectors with watchdog functions incorporating CMOS process technology.

The series consist of a reference voltage source, delay circuit, comparator, and output driver. With the built-in delay circuit, the series do not require any external components to output signals with release delay time. The output type is VDFL low when detected. The EN/ENB pin can control ON and OFF of the watchdog functions. By setting the EN/ENB pin to low or high level, the watchdog function can be OFF while the voltage detector remains operation. Since the EN/ENB pin of the XD6122 and XD6124 series is internally pulled up to the VIN pin or pulled down to the VIN pin, these series can be used with the EN/ENB pin left open when the watchdog functions is used.

The detect voltages are 1.6V, 2.2V, 2.3V, 2.4V, 2.9V, 3.0V, 3.1V, 4.4V, 4.5V, 4.6V, using laser trimming technology.

Six watchdog timeout periods are available in a range from 50ms to 1.6s. Five release delay times are available in a range from 3.13ms to 400ms.

#### APPLICATIONS

- Microprocessor watchdog monitoring and reset circuits

- Memory battery backup circuits

- System power-on reset circuits

- Power failure detection

### **■**FEATURES

**Detect Voltage Range** : 1.6V, 2.2V, 2.3V, 2.4V, 2.9V, **(Standard)** 3.0V, 3.1V, 4.4V, 4.5V, 4.6V

Hysteresis Width: VDFL x 5% (TYP.)Operating Voltage Range:  $1.0V \sim 6.0V$ Detect Voltage Temperature:  $\pm 100ppm/^{\circ}C$  (TYP.)

**Characteristics**

Output Configuration: N-channel open drainWatchdog Pin: Watchdog input

If watchdog input maintains 'H' or 'L' within the watchdog timeout period, a resel signal is output from the RESETB pin.

**EN/ENB Pin** : When the EN/ENB pin voltage is set to low or high level, the watchdog function

low of high level, the watchdog fund

is forced off.

**Release Delay Time** : 400ms, 200ms, 100ms, 50ms, 3.13ms **Watchdog Timeout Period** : 1.6s,800ms,400ms,200ms,100ms,50ms

Operating Ambient Temperature :  $-40^{\circ}$ C ~  $85^{\circ}$ C Package : SOT-25

Environmentally Friendly : EU RoHS Compliant, Pb Free

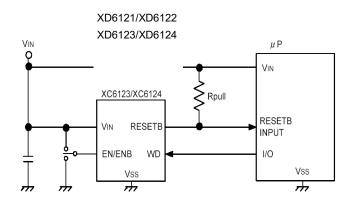

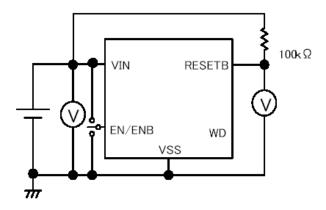

## **■ TYPICAL APPLICATION CIRCUIT**

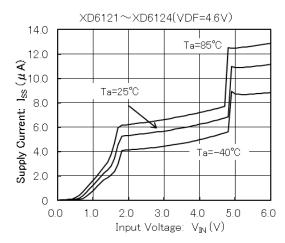

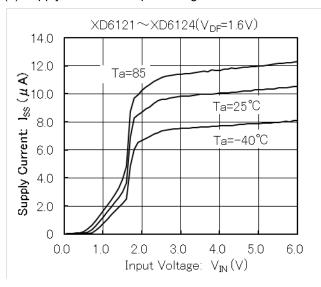

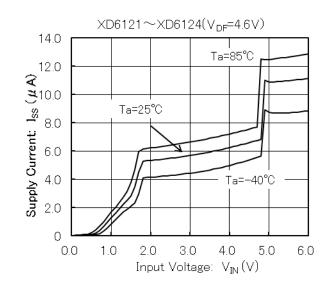

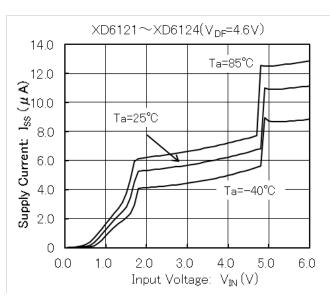

# ■TYPICAL PERFORMANCE CHARACTERISTICS

Supply Current vs. Input Voltage

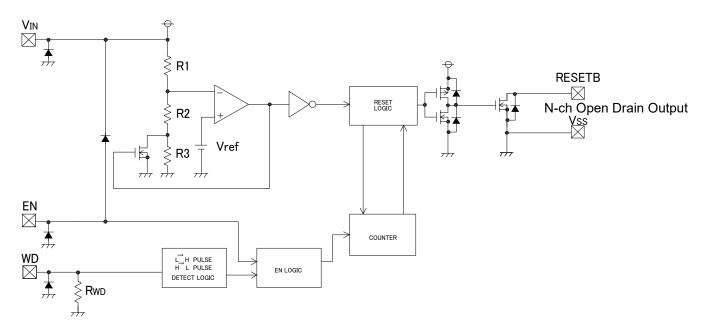

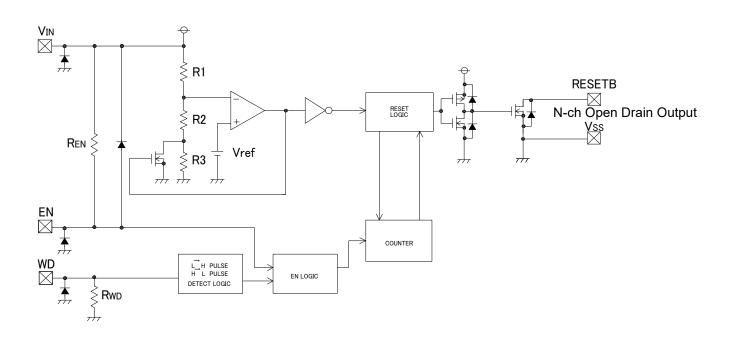

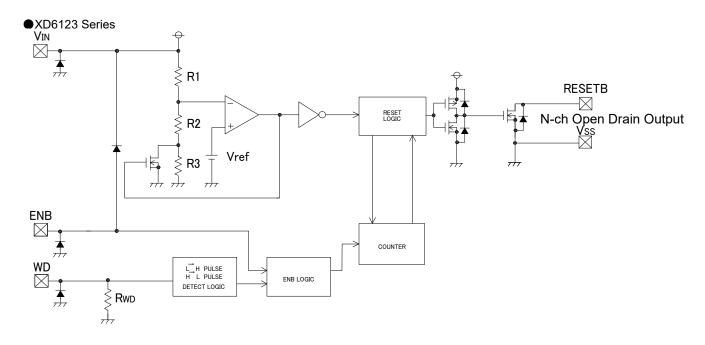

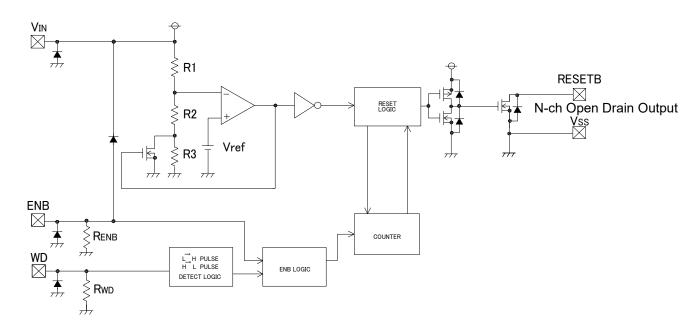

## ■BLOCK DIAGRAMS

#### ●XD6121 Series

#### ●XD6122 Series

## ■BLOCK DIAGRAMS (Continued)

#### ●XD6124 Series

## XD6121/XD6122/XD6123/XD6124 Series

## ■PRODUCT CLASSIFICATION

#### Selection Guide

|        | RESET OL               | JTPUT               |                              | EN/ENB PIN   | FUNCTION          |

|--------|------------------------|---------------------|------------------------------|--------------|-------------------|

| SERIES | \/ (DECETD) (*1)       | Vocu (DESET)        | HYSTERESIS                   | EN/ENB Input | Pull-Up or Down   |

|        | VDFL (RESETB) (*1)     | VDFH (RESET)        |                              | Logic (*2)   | Resistor          |

| VD6404 | N shannel onen drein   |                     |                              | ΓN           | With No Pull-Up   |

| XD6121 | N-channel open drain   | -                   |                              | EN           | Resistor          |

| XD6122 | N shannal anan drain   |                     |                              | EN           | With Pull-Up      |

| XD6122 | N-channel open drain   | -                   | Available:                   | EIN          | Resistor          |

| XD6123 | N shannal anan drain   |                     | V <sub>DFL</sub> x 5% (TYP.) | ENB          | With No Pull-Down |

| XD0123 | N-channel open drain - | -                   |                              | EIND         | Resistor          |

| XD6124 | N shannal anon drain   | Labarrat area drain |                              | ENB          | With Pull-Down    |

| AD0124 | N-channel open drain   |                     |                              | EIND         | Resistor          |

<sup>(\*1)</sup> The output type of RESETB is set to L level at the time of detection.

ENB input logic: The watchdog function turns on when the ENB pin becomes low level.

### Ordering Information

| DESIGNATOR          | ITEM                    | SYMBOL             | DESCRIPTION            |  |

|---------------------|-------------------------|--------------------|------------------------|--|

|                     |                         | А                  | 3.13ms (TYP.)          |  |

|                     |                         | С                  | 50ms (TYP.)            |  |

| 1                   | Release Delay Time(*1)  | D                  | 100ms (TYP.)           |  |

|                     |                         | Е                  | 200ms (TYP.)           |  |

|                     |                         | F                  | 400ms (TYP.)           |  |

|                     | Watchdog Timeout Period | 2                  | 50ms (TYP.)            |  |

|                     |                         | 3                  | 100ms (TYP.)           |  |

|                     |                         | 4                  | 200ms (TYP.)           |  |

| 2                   |                         | 5                  | 400ms (TYP.)           |  |

|                     |                         | 6                  | 1.6s (TYP.)            |  |

|                     |                         | 7                  | 800ms (TYP.)           |  |

| 34                  | Datast Valtage          | 16,22,23,24,29,    | Detect voltage         |  |

| 3/4/                | Detect Voltage          | 30,31,44,45,46(*2) | ex.) 4.5V: ③⇒4, ④⇒5    |  |

| \$6-\(\bar{7}\)(*3) | Package                 | MR-Q               | SOT-25 (3,000pcs/Reel) |  |

| 30-1/(3)            | (Order Unit)            | IVIN-Q             | 301-20 (3,000pcs/Reel) |  |

<sup>(\*1)</sup> Please set the release delay time shorter than or equal to the watchdog timeout period. ex.) XD6123F523MR or XD6123F623MR

<sup>(\*2)</sup> EN input logic: The watchdog function turns on when the EN pin becomes high level.

<sup>(\*2)</sup> For other output voltages, please contact your local Torex sales office or representative. The output voltage optional range is 1.6V to 5.0V.

<sup>(\*3)</sup> The "-Q" suffix denotes "AEC-Q100" and "Halogen and Antimony free" as well as being fully EU RoHS compliant.

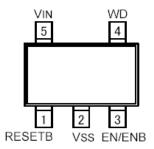

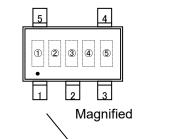

## **■PIN CONFIGURATION**

SOT-25 (TOP VIEW)

## **■ PIN ASSIGNMENT**

| PIN NUMBER | PIN NAME          | FUNCTIONS               |

|------------|-------------------|-------------------------|

| SOT-25     | T II V I V II VIE | renemen                 |

| 1          | RESETB            | Reset Output            |

| 2          | Vss               | Ground                  |

| 3          | EN/ENB            | Watchdog ON/OFF Control |

| 4          | WD                | Watchdog                |

| 5          | V <sub>IN</sub>   | Power Input             |

## **■PIN LOGIC CONDITIONS**

| PIN NAME | LOGIC | CONDITIONS                                                                       |

|----------|-------|----------------------------------------------------------------------------------|

| V        | Н     | V <sub>IN</sub> <u>≥</u> V <sub>DFL</sub> +V <sub>HYS</sub>                      |

| Vin      | L     | V <sub>IN</sub> <u>≤</u> V <sub>DFL</sub>                                        |

| EN/END   | Н     | V <sub>EN</sub> /V <sub>ENB</sub> ≧1.30V                                         |

| EN/ENB   | L     | V <sub>EN</sub> /V <sub>ENB</sub> ≦0.35V                                         |

|          | Н     | The state maintaining WD <u>≥</u> V <sub>WDH</sub> for more than t <sub>WD</sub> |

| NA/D     | L     | The state maintaining WD <u>≤</u> V <sub>WDL</sub> for more than t <sub>WD</sub> |

| WD       | L→H   | Vwdl→Vwdh, 300ns≦twdin≦twd                                                       |

|          | H→L   | V <sub>WDH</sub> →V <sub>WDL</sub> , 300ns≦t <sub>WDIN</sub> ≦t <sub>WD</sub>    |

#### NOTE:

V<sub>DFL</sub>: Detect Voltage

V<sub>HYS</sub>: Hysteresis Range

V<sub>WDH</sub>: WD High Level Voltage

V<sub>WDL</sub>: WD Low Level Voltage

t<sub>WDIN</sub>: WD Pulse Width

t<sub>WD</sub>: WD Timeout Period

For the details of each parameter, please see the electrical characteristics.

### **■**FUNCTION CHART

| VIN  | XD6121/XD6122   | XD6123/XD6124 | $V_{\mathrm{WD}}$ | Vresetb (*2) |  |   |                                      |

|------|-----------------|---------------|-------------------|--------------|--|---|--------------------------------------|

| VIIN | V <sub>EN</sub> | $V_{ENB}$     | VVVD              | V RESETB V   |  |   |                                      |

|      |                 |               | Н                 |              |  |   |                                      |

| Н    | ш               | ш             |                   | 1            |  | L | Repeating detect and release (H→L→H) |

| "    | Н               |               | OPEN              |              |  |   |                                      |

|      |                 |               | L⇔H               | Н            |  |   |                                      |

| Н    |                 | Н             | *1                | Н            |  |   |                                      |

| L    | L               | L             | '                 | L            |  |   |                                      |

#### NOTF:

- \*1: Including all logics of the WD ( $V_{WD}$ =H, L, OPEN, H $\rightarrow$ L, L $\rightarrow$ H).

- \*2: When the VRESETB is High, the circuit is in the release state. When the VRESETB is Low, the circuit is in the detection state.

- \*3: V<sub>IN</sub>=L and V<sub>EN</sub>/V<sub>ENB</sub>=H cannot be combined because the rated input voltage of the EN/ENB pin is V<sub>ss</sub>-0.3V to V<sub>IN</sub>+0.3V.

- \*4: The RESETB pin becomes indefinite operation while 0.35V<V<sub>EN</sub>/V<sub>ENB</sub><1.3V.

- \*5: The EN pin of the XD6121 series is not internally pulled up. When using the watchdog function, please drive the V<sub>EN</sub> pin in high level. The EN pin of the XD6122 series is internally pulled up. The watchdog function can be used even the EN pin left open. The ENB pin of the XD6123 series is not internally pulled down. When using the watchdog function, please drive the V<sub>ENB</sub> pin in low level. The ENB pin of the XD6124 series is internally pulled up. The watchdog function can be used even the ENB pin left open.

### ■ ABSOLUTE MAXIMUM RATINGS

| PARAMET                       | ER                       | SYMBOL             | RATINGS                                             | UNITS |  |

|-------------------------------|--------------------------|--------------------|-----------------------------------------------------|-------|--|

|                               |                          | V <sub>IN</sub>    | -0.3 ~ 7.0                                          | V     |  |

| Input Volta                   | Input Voltage            |                    | -0.3 ~ V <sub>IN</sub> + 0.3 or 7.0 <sup>(*1)</sup> | V     |  |

|                               |                          | V <sub>WD</sub>    | VwD -0.3 ~ 7.0                                      |       |  |

| RESETB Pin Voltage            |                          | I <sub>RBOUT</sub> | 20                                                  | mA    |  |

| RESETB Pin \                  | RESETB Pin Voltage       |                    | -0.3 ~ 7.0                                          | V     |  |

| Danna Dia aire ati are        |                          |                    | 250                                                 |       |  |

| '                             | Power Dissipation SOT-25 |                    | 600 (40mm x 40mm Standard board) (*2)               | mW    |  |

| (Ta=25℃)                      |                          |                    | 760 (JESD51-7 board) <sup>(*2)</sup>                |       |  |

| Operating Ambient Temperature |                          | Topr               | -40 ~ 85                                            | οС    |  |

| Storage Temperature           |                          | Tstg               | -55 ~ 125                                           | οС    |  |

$<sup>^{(*1)}</sup>$  The maximum value should be either  $V_{IN}$  + 0.3V or 7.0V in the lowest.

Please refer to PACKAGING INFORMATION for the mounting condition.

<sup>(\*2)</sup> The power dissipation figure shown is PCB mounted and is for reference only.

## ■ ELECTRICAL CHARACTERISTICS

Ta=25 °C

| PARAMETER                                              | SYMBOL          |                                                                                                                                           | COND                                                           | ITIONS                                                                     | MIN.                       | TYP.                    | MAX.                    | UNITS | CIRCUIT    |

|--------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|-------------------------|-------------------------|-------|------------|

|                                                        |                 | V <sub>EN</sub> =V <sub>SS</sub>                                                                                                          |                                                                |                                                                            | V <sub>DFL(T)</sub> × 0.98 | VDFL(T)                 | VDFL(T)×<br>1.02        |       |            |

| Detect Voltage                                         | VDFL            |                                                                                                                                           |                                                                | -40°C <u>≤</u> Topr <u>≤</u> 85 °C                                         | V <sub>DFL(T)</sub> × 0.96 | VDFL(T)                 | VDFL(T)×<br>1.04        | V     | 1          |

|                                                        |                 | V <sub>EN</sub> =V <sub>SS</sub>                                                                                                          | V <sub>EN</sub> =V <sub>SS</sub>                               | 1                                                                          | V <sub>DFL</sub> × 0.02    | V <sub>DFL</sub> × 0.05 | V <sub>DFL</sub> × 0.08 |       | _          |

| Hysteresis Width                                       | VHYS            |                                                                                                                                           |                                                                | -40°C < Topr < 85 °C                                                       | $V_{DFL}$                  | V <sub>DFL</sub>        | V <sub>DFL</sub>        | V     | 1          |

|                                                        |                 | WD=OPEN, V                                                                                                                                | /IN=VDEI                                                       |                                                                            | × 0.01                     | × 0.05                  | × 0.08                  |       |            |

|                                                        |                 |                                                                                                                                           | IIV V DIT                                                      | , ,                                                                        |                            |                         | 20                      |       |            |

|                                                        |                 |                                                                                                                                           |                                                                | -40°C <u>≤</u> Topr <u>≤</u> 85 °C                                         | -                          | -                       | -                       |       |            |

| Supply Current (*1)                                    | Iss             | WD=OPEN, V                                                                                                                                | / <sub>IN</sub> =V <sub>DFI</sub>                              |                                                                            | -                          | 10                      | 16                      | μA    | 1          |

|                                                        |                 |                                                                                                                                           |                                                                | -40°C <u>≤</u> Topr <u>&lt;</u> 85 °C                                      | -                          | -                       | 28                      |       |            |

|                                                        |                 | WD=OPEN, V                                                                                                                                | / <sub>IN</sub> =6.0\                                          |                                                                            | -                          | 12                      | 18                      |       |            |

|                                                        |                 |                                                                                                                                           |                                                                | -40°C <u>≤</u> Topr <u>≤</u> 85°C                                          | -                          | -                       | 35                      |       |            |

| Operating Voltage                                      | VIN             |                                                                                                                                           |                                                                | -40°C <u>≤</u> Topr <u>&lt;</u> 85 °C                                      | 1.0                        | -                       | 6.0                     | V     | 1          |

|                                                        |                 |                                                                                                                                           |                                                                | VIN=1.0V                                                                   | 0.15                       | 0.5                     | -                       |       |            |

| Output Current                                         | IRBOUT          | N-ch.                                                                                                                                     |                                                                | 2.0V (V <sub>DFL(T)</sub> > 2.0V)                                          | 2.0                        | 2.5                     | -                       | mA    | 3          |

| '                                                      |                 | VDS=0.5V                                                                                                                                  |                                                                | 3.0V (V <sub>DFL(T)</sub> >3.0V)                                           | 3.0                        | 3.5                     | -                       |       |            |

|                                                        |                 |                                                                                                                                           | V <sub>IN</sub> =                                              | 4.0V (V <sub>DFL(T)</sub> >4.0V)                                           | 3.5                        | 4.0                     | -                       |       |            |

|                                                        |                 |                                                                                                                                           |                                                                |                                                                            | 2.00                       | 3.13                    | 5.00                    |       |            |

| Release Delay Time                                     | t <sub>DR</sub> | Time until V <sub>I</sub> N is increased from 1.0V to 2.0V and attains to the release time level, and the Reset output pin releases.      |                                                                | 37                                                                         | 50                         | 63                      | ms                      | 4     |            |

| (V <sub>DFL</sub> ≤1.8V)                               |                 |                                                                                                                                           |                                                                | 75                                                                         | 100                        | 125                     |                         |       |            |

|                                                        |                 |                                                                                                                                           |                                                                | 150                                                                        | 200                        | 250                     |                         |       |            |

|                                                        |                 |                                                                                                                                           |                                                                |                                                                            | 300                        | 400                     | 500                     |       |            |

|                                                        | t <sub>DR</sub> | Time a small N . in in any a                                                                                                              |                                                                | oagad from                                                                 | 2.00                       | 3.13                    | 5.00                    | ms    | <b>4</b> ) |

| Release Delay Time                                     |                 | Time until V <sub>IN</sub> is in 1.0V to (V <sub>DFL</sub> x 1.1                                                                          | I V <sub>IN</sub> is increased from<br>/ <sub>DFL</sub> x 1.1) | 37                                                                         | 50                         | 63                      |                         |       |            |

| (V <sub>DFL</sub> ≥1.9V)                               |                 | and attains to the release time level,<br>and the Reset output pin releases.                                                              |                                                                | lease time level,                                                          | 75                         | 100                     | 125<br>250              |       | 4          |

|                                                        |                 |                                                                                                                                           |                                                                | 150<br>300                                                                 | 200<br>400                 | 500                     |                         |       |            |

|                                                        |                 | Time until \/                                                                                                                             | io doo                                                         | rooped from 6.0\/ to                                                       | 300                        | 400                     | 300                     |       |            |

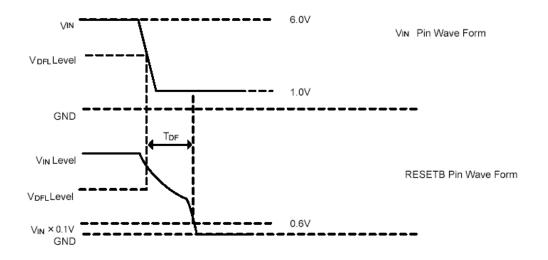

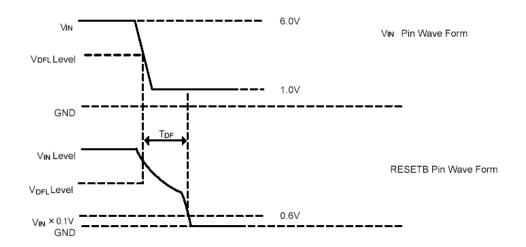

| Detect Delay Time                                      | t <sub>DF</sub> | 1.0V and atta                                                                                                                             | ains to t<br>e Reset                                           | reased from 6.0V to<br>the detect voltage<br>output pin detects<br>t open. | -                          | 5.5                     | 33                      | μs    | 4          |

| V <sub>DFL</sub><br>Leakage Current                    | ILEAK           | V <sub>IN</sub> =6.0V, V <sub>R</sub>                                                                                                     | ESETB=6                                                        | 5.0V                                                                       | -                          | 0.01                    | 0.1                     | μA    | 3          |

|                                                        |                 |                                                                                                                                           |                                                                |                                                                            | 37                         | 50                      | 63                      |       |            |

|                                                        |                 | Time until V <sub>I</sub>                                                                                                                 | √ increa                                                       | ises form                                                                  | 75                         | 100                     | 125                     | ms    |            |

| Watchdog<br>Timeout Period<br>(V <sub>DFL</sub> ≤1.8V) | t <sub>wD</sub> | 1.0V to 2.0V                                                                                                                              | and                                                            |                                                                            | 150                        | 200                     | 250                     |       | (5)        |

|                                                        | LVVD            |                                                                                                                                           |                                                                | is released to go                                                          | 300                        | 400                     | 500                     |       |            |

| , _ ,                                                  |                 | into the detection state. (WD=OPEN)                                                                                                       |                                                                | 600                                                                        | 800                        | 1000                    |                         |       |            |

|                                                        |                 |                                                                                                                                           |                                                                |                                                                            | 1200                       | 1600                    | 2000                    |       |            |

|                                                        |                 |                                                                                                                                           |                                                                |                                                                            | 37                         | 50                      | 63                      |       |            |

| Watchdog<br>Timeout Period                             |                 | Time until $V_{IN}$ increases from 1.0V to $(V_{DFL}x1.1)$ and the Reset output pin is released to go into the detection state. (WD=OPEN) |                                                                | ses from                                                                   | 75                         | 100                     | 125                     | - ms  |            |

|                                                        | two             |                                                                                                                                           |                                                                | akaning ing perterengan 199                                                | 150                        | 200                     | 250                     |       | ⑤          |

| (V <sub>DFL</sub> ≥1.9V)                               |                 |                                                                                                                                           |                                                                |                                                                            | 300                        | 400                     | 500                     |       |            |

|                                                        |                 |                                                                                                                                           |                                                                | 1 Julio. (VVD-01 LIV)                                                      | 600                        | 800                     | 1000                    |       |            |

|                                                        |                 |                                                                                                                                           |                                                                |                                                                            | 1200                       | 1600                    | 2000                    |       |            |

## ■ ELECTRICAL CHARACTERISTICS (Continued)

Ta=25 °C

| PARAMETER                        | SYMBOL                              | CONDIT                                                                                             | IONS                                  | MIN.                  | TYP. | MAX.                  | UNITS | CIRCUIT |

|----------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|------|-----------------------|-------|---------|

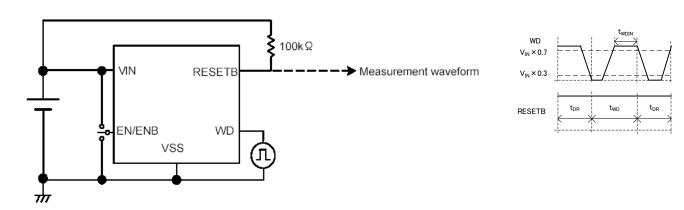

| Watchdog<br>Minimum Pulse Width  | t <sub>WDIN</sub>                   | V <sub>IN</sub> =6.0V,<br>Apply pulse from 6.0V to 0V to the WD<br>pin.                            |                                       | 300                   | -    | -                     | ns    | 6       |

| Watchdog<br>High Level Voltage   | V <sub>WDH</sub>                    | V <sub>IN</sub> =V <sub>DF</sub> L x 1.1V ~ 6.0V                                                   | -40°C ≤ Topr ≤ 85 °C                  | V <sub>IN</sub> x 0.7 | -    | 6                     | V     | 6       |

| Watchdog<br>Low Level Voltage    | V <sub>WDL</sub>                    | V <sub>IN</sub> =V <sub>DFL</sub> x 1.1V ~ 6.0V                                                    | -40°C <u>≤</u> Topr <u>&lt;</u> 85 °C | 0                     | -    | V <sub>IN</sub> x 0.3 | V     | 6       |

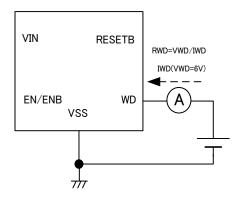

| Watchdog<br>Pull-down Resistance | R <sub>WD</sub>                     | V <sub>WD</sub> =6V, R <sub>WD</sub> =V <sub>WD</sub> /I <sub>WD</sub>                             |                                       | 300                   | 600  | 900                   | kΩ    | 7       |

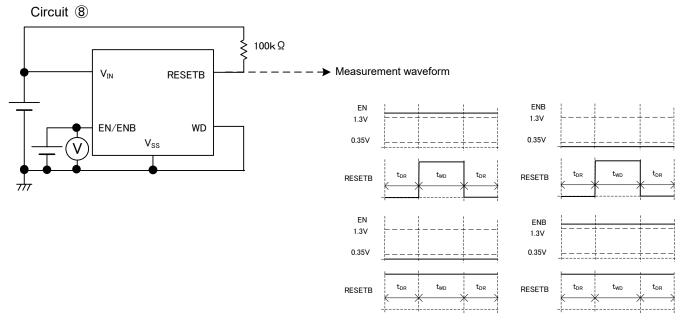

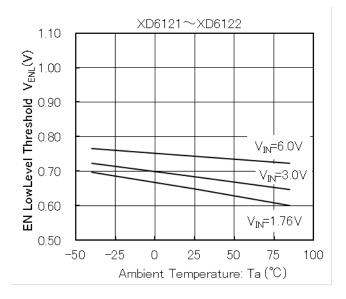

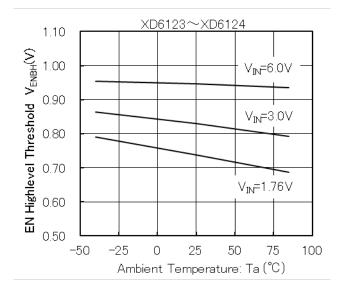

| EN/ENB<br>High Level Voltage     | V <sub>ENH</sub> /V <sub>ENBH</sub> | V <sub>IN</sub> =V <sub>DFL</sub> x 1.1V ~ 6.0V                                                    | -40°C ≤ Topr <u>&lt;</u> 85 °C        | 1.3                   | -    | Vin                   | V     | 8       |

| EN/ENB<br>Low Level Voltage      | V <sub>ENL</sub> /V <sub>ENBL</sub> | V <sub>IN</sub> =V <sub>DFL</sub> x 1.1V ~ 6.0V                                                    | -40°C <u>≤</u> Topr <u>&lt;</u> 85 °C | 0                     | -    | 0.35                  | V     | 8       |

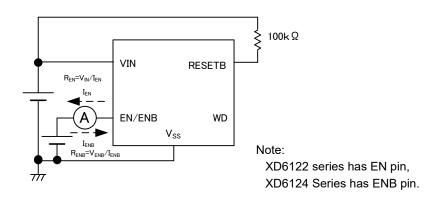

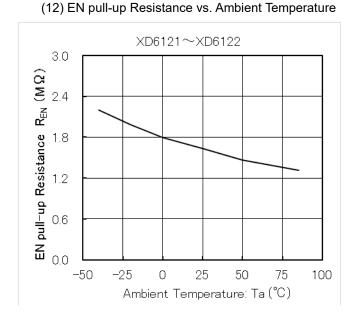

| EN Pull-up<br>Resistance (*2)    | Ren                                 | V <sub>IN</sub> =6.0V, V <sub>EN</sub> =0V, R <sub>EN</sub> =V <sub>IN</sub> / I <sub>EN</sub>     |                                       | 1.0                   | 1.6  | 2.4                   | ΜΩ    | (9)     |

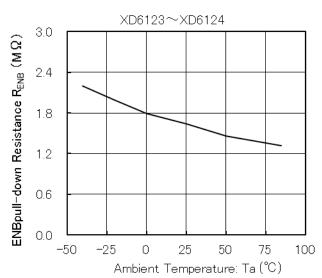

| ENB Pull-down<br>Resistance (*3) | R <sub>ENB</sub>                    | V <sub>IN</sub> =6.0V, V <sub>ENB</sub> =6V, R <sub>ENB</sub> =V <sub>ENB</sub> / I <sub>ENB</sub> |                                       | 1.0                   | 1.0  | 2.4                   | 17177 | 3       |

#### NOTE

The EN/ENB pin is CMOS input. For the XD6122 (pull-up resistor) and XD6124 (pull-down resistor), supply current increases in the following values when the watchdog function is OFF.

XD6122 Series :  $(V_{IN}\text{-}V_{EHL})/1.6M\Omega$  (TYP.) XD6124 Series :  $V_{EHBH}/1.6M\Omega$  (TYP.)

<sup>\*</sup> In case where no EN/ENB pin's condition written in the test condition field,  $V_{EN}=V_{IN}$  and  $V_{ENB}=V_{SS}$ .

<sup>\*\*</sup> V<sub>DFL (T)</sub> =Setting detect voltage value

<sup>\*\*\*</sup> The values for -40°C $\leq$ Ta $\leq$ 85°C are designed values.

<sup>(\*1)</sup> The condition when the watchdog pin is ON.

$<sup>\</sup>ensuremath{^{(^*2)}}$  For the XD6122 series only.

<sup>(\*3)</sup> For the XD6124 series only.

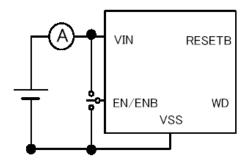

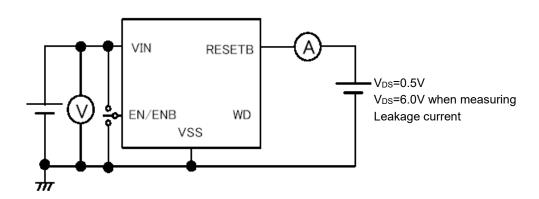

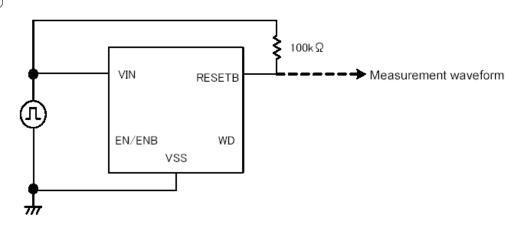

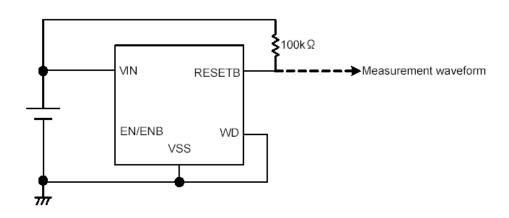

## **■**TEST CIRCUITS

## Circuit ①

### Circuit 2

### Circuit ③

## ■TEST CIRCUITS (Continued)

### Circuit 4

### Circuit ⑤

### Circuit ⑥

## ■TEST CIRCUITS (Continued)

### Circuit 7

Note: The above reference is about the EN/ENB logic operation.

#### Circuit (9)

## XD6121/XD6122/XD6123/XD6124 Series

### ■ OPERATIONAL EXPLANATION

The XD6121/6122/6123/6124 series compare, using the error amplifier, the voltage of the internal voltage reference source with the voltage divided by R1, R2 and R3 connected to the  $V_{IN}$  pin. The resulting output signal from the error amplifier activates the watchdog logic, delay circuit and the output driver. When the  $V_{IN}$  pin voltage gradually falls and finally reaches the detect voltage, the RESETB pin output goes from high to low in the case of the  $V_{DFL}$  type ICs.

#### <RESETB / RESET Pin Output Signal>

\* V<sub>DFL</sub> (RESETB) type - output signal: Low when detected.

The RESETB pin output goes from high to low whenever the  $V_{IN}$  pin voltage falls below the detect voltage. The RESETB pin remains low for the release delay time ( $t_{DR}$ ) after the  $V_{IN}$  pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the RESETB pin output remains low for the release delay time ( $t_{DR}$ ), and thereafter the RESET pin outputs high level signal.

#### <Hysteresis>

When the internal comparator output is high, the NMOS transistor connected in parallel to R3 is turned ON, activating the hysteresis circuit. The difference between the release and detect voltages represents the hysteresis width, as shown by the following calculations:

$V_{DFL}$  (detect voltage) = (R1+R2+R3) x Vref / (R2+R3)  $V_{DR}$  (release voltage) = (R1+R2) x Vref / (R2)  $V_{HYS}$  (hysteresis width) = $V_{DR}$ - $V_{DFL}$  (V)  $V_{DR} > V_{DFL}$

- \* Please refer to the block diagrams for R1, R2, R3 and Vref.

- \* Hysteresis width is selectable from VDFL x 0.05V (TYP.).

#### <Watchdog (WD) Pin>

The series use a watchdog timer to detect malfunction or "runaway" of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB pin output maintains the detection state for the release delay time (t<sub>DR</sub>), and thereafter the RESETB pin outputs low to high signal.

The watchdog pin is pulled down to the V<sub>SS</sub> internally. When the watchdog pin is not connected, A reset signal comes out after the watchdog timeout period.

Six watchdog timeout period settings (twD) are available in 1.6s, 800ms, 400ms, 200ms, 100ms, and 50ms.

#### <EN Pin>

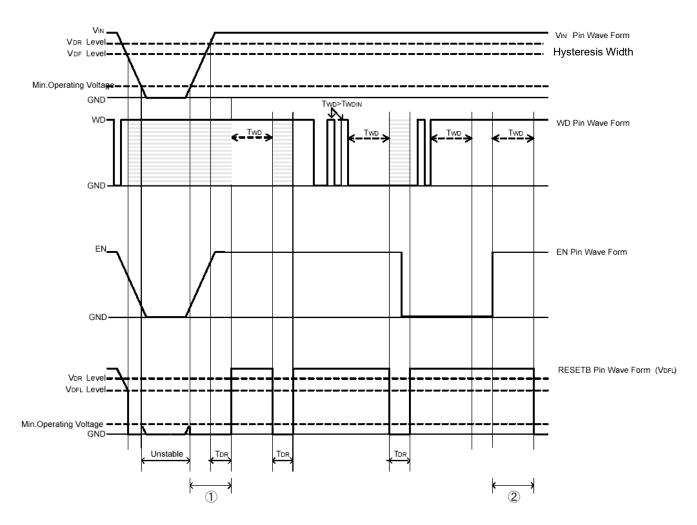

In case where the watchdog function is not used, When the EN pin input driven to low level, only the watchdog function is forced off while the detect voltage circuit remains operation. For using the watchdog function, the EN pin should be used in high level. Even after the input voltage and the EN pin voltage are driven back high, the RESETB pin output maintains the detection state for the release delay time ( $T_{DR}$ ). (Refer to the TIMING CHART 1-①.)

The watchdog function recovers immediately when the input voltage becomes higher than the release voltage and the EN pin voltage driven from low to high level. (Refer to the TIMING CHART 1-2.)

A diode, which is an input protection element, is connected between the EN pin and  $V_{IN}$  pin. Therefore, if the EN pin is applied voltage that exceeds  $V_{IN}$ , the current will flow to  $V_{IN}$  through the diode. For avoiding any damage to the IC, please use this IC within the stated maximum ratings ( $V_{SS}$ -0.3V  $\sim V_{IN}$ +0.3V) on the EN pin.

#### <ENB Pin>

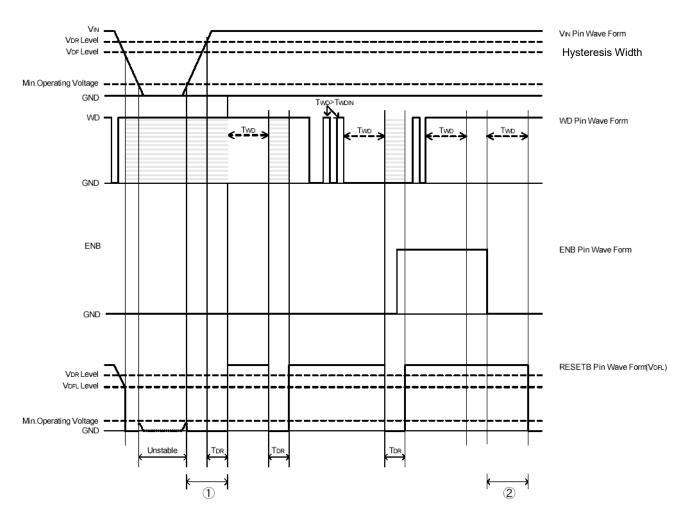

In case where the watchdog function is not used, when the ENB pin input driven to high level, only the watchdog function is forced off while the detect voltage circuit remains operation. For using the watchdog function, the ENB pin should be used in low level. Even after the input voltage and the ENB pin voltage are driven back low, the RESETB pin output maintains the detection state for the release delay time (t<sub>DR</sub>). (Refer to the TIMING CHART 2-①.)

The watchdog function recovers immediately when the input voltage becomes higher than the release voltage and the ENB pin voltage driven from high to low level. (Refer to the TIMING CHART 2-②.)

A diode, which is an input protection element, is connected between the ENB pin and  $V_{IN}$  pin. Therefore, if the ENB pin is applied voltage that exceeds  $V_{IN}$ , the current will flow to  $V_{IN}$  through the diode. For avoiding any damage to the IC, please use this IC within the stated maximum ratings ( $V_{SS}$ -0.3V ~  $V_{IN}$ +0.3V) on the ENB pin.

#### <Release Delay Time>

Release delay time ( $t_{DR}$ ) is the time that elapses from when the  $V_{IN}$  pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WD pin, until the RESETB pin output is released from the detection state. Five release delay time ( $t_{DR}$ ) watchdog timeout period settings are available in 400ms, 200ms, 100ms, 50ms, and 3.13ms.

#### <Detect Delay Time>

Detect Delay Time (t<sub>DF</sub>) is the time that elapses from when the V<sub>IN</sub> pin voltage falls to the detect voltage until the RESETB pin output goes into the detection state.

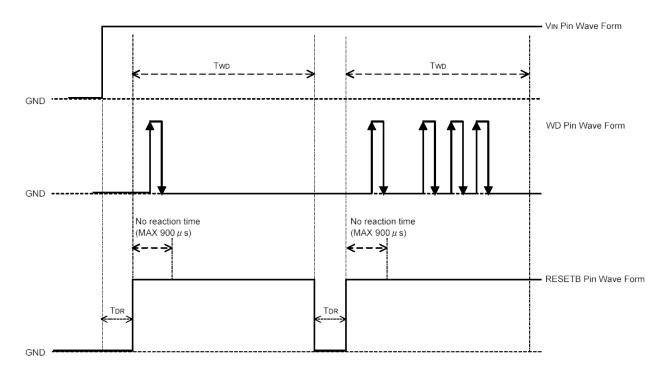

## **■**TIMING CHARTS

- 1. XD6121/XD6122 Series (EN products)

- ●N-ch Open Drain Output (Rpull=100kΩ)

●t<sub>DF</sub> (N-ch Open Drain Output, Rpull=100kΩ)

## ■TIMING CHARTS (Continued)

- 2. XD6123/XD6124 Series (ENB products)

- •N-ch Open Drain Output (Rpull=100kΩ)

•tof (N-ch Open Drain Output, Rpull=100k $\Omega$ )

### ■NOTES ON USE

- 1. Please use this IC within the stated maximum ratings. For temporary, transitional voltage drop or voltage rising phenomenon, the IC is liable to malfunction should the ratings be exceeded.

- 2. When a resistor is connected between the V<sub>IN</sub> pin and the input, the V<sub>IN</sub> voltage drops while the IC is operating and a malfunction may occur as a result of the IC's through current.

- 3. In order to stabilize the IC's operations, please ensure that the  $V_{IN}$  pin's input frequency's rise and fall times are more than  $1\mu s/V$ .

- 4. Noise at the power supply may cause a malfunction of the watchdog operation or the voltage detector. In such case, please strength V<sub>IN</sub> and GND lines. Also, please connect a capacitor such as 0.22μF between the V<sub>IN</sub> pin and the GND pin and evaluate the device on the actual board carefully before use.

- 5. Protecting against a malfunction while the watchdog time out period, an ignoring time (no reaction time) occurs to the rise and fall times. Referring to the figure below, the ignoring time (no reaction time) lasts for 900µs at maximum. (refer to the Figure1 below)

- 6. The EN pin of the XD6121 series is not internally pulled up. When using the watchdog function, please drive the V<sub>EN</sub> pin in high level. The EN pin of the XD6122 series is internally pulled up. The watchdog function can be used even the EN pin left open. The ENB pin of the XD6123 series is not internally pulled down. When using the watchdog function, please drive the V<sub>ENB</sub> pin in low level. The ENB pin of the XD6124 series is internally pulled down. The watchdog function can be used even the ENB pin left open.

- 7. Torex places an importance on improving our products and its reliability.

However, by any possibility, we would request user fail-safe design and post-aging treatment on system or equipment.

## ■TYPICAL PERFORMANCE CHARACTERISTICS

#### (1) Supply Current vs. Input Voltage

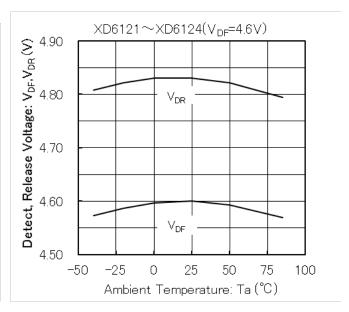

#### (2) Ambient Temperature vs. Detect Release Voltage

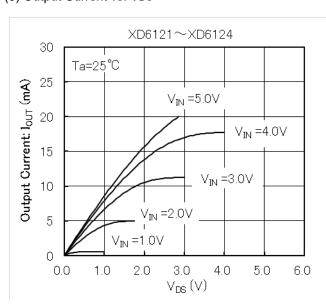

#### (3) Output Current vs. VDS

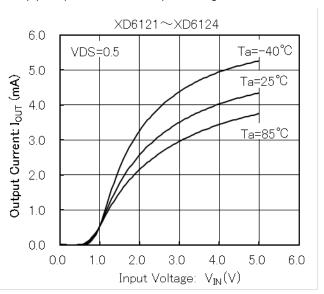

#### (4) Output Current vs. Input Voltage

## ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

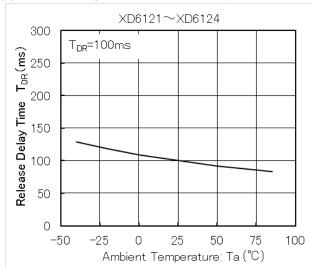

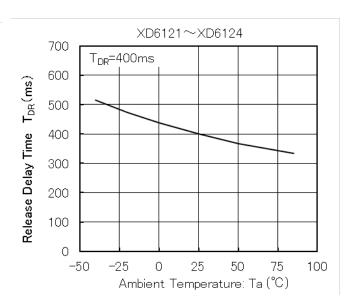

#### (5) Release Delay Time vs. Ambient Temperature

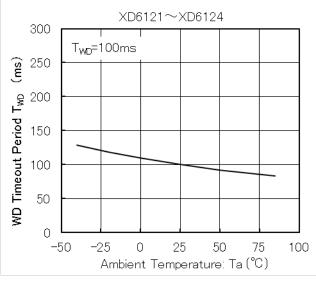

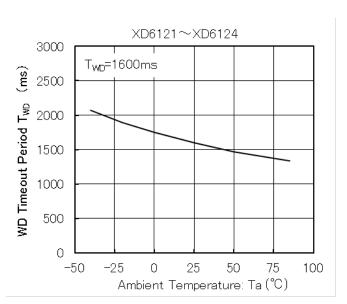

#### (6) WD Timeout Period vs. Ambient Temperature

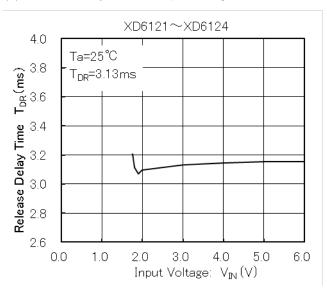

#### (7) Release Delay Time vs. Input Voltage

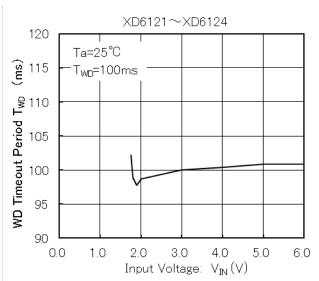

(8) WD Timeout Period vs. Input Voltage

TOIREX

## XD6121/XD6122/XD6123/XD6124 Series

## ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

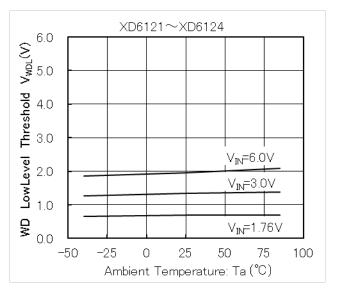

#### (9) WD Low Level Voltage vs. Ambient Temperature

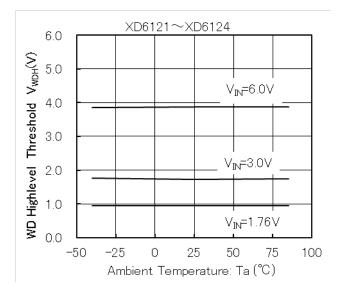

#### (10) WD High Level Voltage vs. Ambient Temperature

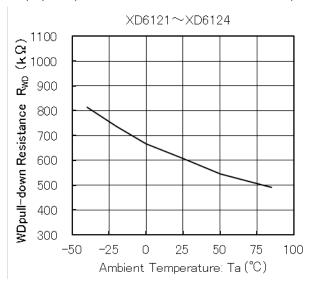

(11) WD pull-down Resistance vs. Ambient Temperature

### (13) ENB pull-up Resistance vs. Ambient Temperature

## ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

#### (14) EN Low Level Voltage vs. Ambient Temperature

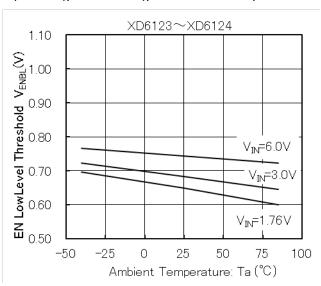

#### (16) ENB Low Level Voltage vs. Ambient Temperature

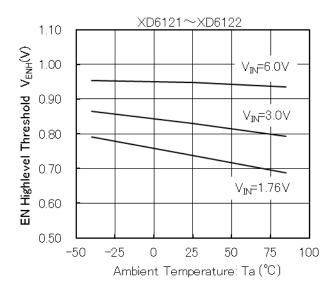

#### (15) EN High Level Voltage vs. Ambient Temperature

#### (17) ENB High Level Voltage vs. Ambient Temperature

## XD6121/XD6122/XD6123/XD6124 Series

## **■**PACKAGING INFORMATION

For the latest package information go to, <a href="www.torexsemi.com/technical-support/packages">www.torexsemi.com/technical-support/packages</a>

| PACKAGE | OUTLINE / LAND PATTERN | THERMAL CHARACTERISTICS  |

|---------|------------------------|--------------------------|

| SOT-25  | SOT-25 PKG             | SOT-25 Power Dissipation |

## **■**MARKING RULE

1 represents products series

| MARK | PRODUCT SERIES                      |

|------|-------------------------------------|

| В    | XD6121/XD6122/XD6123/XD6124******-Q |

23 represents internal sequential number.

| MARK | PRODUCT SERIES |

|------|----------------|

| 01   | XD6121A246MR-Q |

| 02   | XD6122C629MR-Q |

| 03   | XD6123C330MR-Q |

| 04   | XD6124E616MR-Q |

| 05   | XD6121C622MR-Q |

| 06   | XD6122C645MR-Q |

| 07   | XD6121C229MR-Q |

| 80   | XD6122C229MR-Q |

| 09   | XD6122C630MR-Q |

| 10   | XD6121A430MR-Q |

| 11   | XD6122C422MR-Q |

| 13   | XD6122A246MR-Q |

SOT-25(Under dot)

45 represents production lot number

01 $\sim$ 09, 0A $\sim$ 0Z, 11 $\sim$ 9Z, A1 $\sim$ A9, AA $\sim$ AZ, B1 $\sim$ ZZ in order.(G, I, J, O, Q, W excluded)

<sup>\*</sup> No character inversion used.

- 1. The product and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. The information in this datasheet is intended to illustrate the operation and characteristics of our products. We neither make warranties or representations with respect to the accuracy or completeness of the information contained in this datasheet nor grant any license to any intellectual property rights of ours or any third party concerning with the information in this datasheet.

- Applicable export control laws and regulations should be complied and the procedures required by such laws and regulations should also be followed, when the product or any information contained in this datasheet is exported.

- 4. The product is neither intended nor warranted for use in equipment of systems which require extremely high levels of quality and/or reliability and/or a malfunction or failure which may cause loss of human life, bodily injury, serious property damage including but not limited to devices or equipment used in 1) nuclear facilities, 2) aerospace industry, 3) medical facilities, 4) automobile industry and other transportation industry and 5) safety devices and safety equipment to control combustions and explosions, excluding when specified for in-vehicle use or other uses.

Do not use the product for in-vehicle use or other uses unless agreed by us in writing in advance.

- 5. Although we make continuous efforts to improve the quality and reliability of our products; nevertheless Semiconductors are likely to fail with a certain probability. So in order to prevent personal injury and/or property damage resulting from such failure, customers are required to incorporate adequate safety measures in their designs, such as system fail safes, redundancy and fire prevention features.

- 6. Our products are not designed to be Radiation-resistant.

- 7. Please use the product listed in this datasheet within the specified ranges.

- 8. We assume no responsibility for damage or loss due to abnormal use.

- 9. All rights reserved. No part of this datasheet may be copied or reproduced unless agreed by Torex Semiconductor Ltd in writing in advance.

TOREX SEMICONDUCTOR LTD.